# Efficient Change System for Vending Machines Using Verilog HDL

# B. Madhavi<sup>1</sup>, K. Suseela<sup>2</sup>, Ankitha Banala<sup>3</sup>, Bhavana Duppati<sup>4</sup>, Deepika Mekala<sup>5</sup>

<sup>1,2</sup> Assistant Professor, <sup>3,4,5</sup> Under Graduation, ECE, School of Engineering and Technology, Sri Padmavati Mahila Visvavidyalayam (Women's University) Mail Id: gysusi@gmail.com

# Abstract:

A vending machine that can efficiently handle change and dispense a variety of goods is designed and implemented in the Vending Machine with Change System using Verilog project. Additionally, the system has intelligent change management features that guarantee clients receive accurate transaction updates. Vending machines are not as common in India as they are in some other nations, but their use has been gradually growing, especially in cities where people want easy access to snacks, drinks, and other necessities. This project investigates the combination of software algorithms for transaction processing and inventory management with hardware elements like coin acceptors, bill validators, and product dispensers. The vending machine system has been rigorously tested and validated to show accuracy, scalability, and dependability in a variety of operating situations. By providing a workable alternative for companies looking for effective and user-friendly vending solutions, the initiative advances automated retail systems.

**Keywords:** Vending Machine, Verilog HDL, Finite State Machine (FSM), FPGA Simulation, Electronic Vending System

# **1.INTRODUCTION**

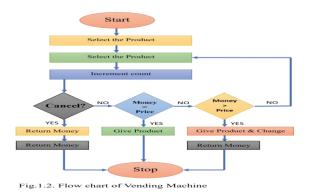

In contemporary times of automation, vending machines now plays a vital role in day to day living by providing quick and easy access to a plethora of products in the forms of snacks, drinks, and other consumer goods. A vital functionality for an efficient vending machine is the ability to not only take user input and dispense the selected product, but also return the accuracy of the change based on the type of coins inserted. The purpose of the presented project is to design and develop a vending machine along with a change return system, in Verilog, a Hardware Description Language (HDL) used widely to describe the modeling of electronic systems. The vending machine will work as a Finite State Machine (FSM) and be used to monitor user input and corner cases such as inserting coins, selecting a product and returning change in an orderly manner using digital logic. The notion for this project will be to simulate a real life vending machine example using Verilog HW Language that will show how to dispense a product and demonstrate how to automatically calculate change. The customer will be able to insert coins (first the denomination in this case) to make a selection and receive expected change when the amount inserted exceeds the price of the selected product. This design and model demonstrate how Verilog can be utilized to model complex, interactive, and time dependant digital systems that you might use on daily basis.

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

### **Related Works**

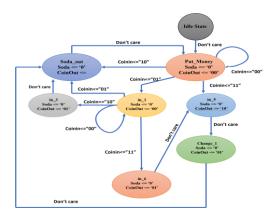

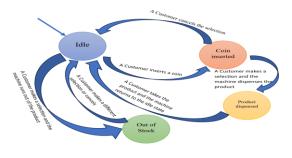

In [1], we present a design and simulation for a vending machine system using Verilog Hardware Description Language (HDL), which we modeled as a Finite State Machine (FSM), a common model used for sequential logic design. The system's implementation uses Mealy machine logic, which means the outputs depend on the current state and input, leading to faster response times for the system. This work is especially relevant as it described a modular and efficient FSM-based vending machine implementing Verilog, and showcased simulation and testing techniques, closely related to experiences in the industry. The design approach in this work could be used as a model for building more complicated vending systems, like vending systems that incorporate multiple products, or digital payments. In [2] This act is a solid example of FSM-based vending systems and expanded upon how behavioral modeling in Verilog can be used effectively to replicate real-world automation systems. The paper is especially useful for students and engineers searching for a simple, yet useful example of vending logic utilized in digital hardware. The system uses a Moore machine model, in which the outputs are determined by the current state alone which can lead to a more stable, repeatable output response which is necessary in a physical hardware case. The vending machine accepts coin denominations of  $\gtrless 1$ ,  $\gtrless 2$ , and  $\gtrless 5$ , and allows the user to select between multiple products. Each state in the FSM represents a specific transaction stage-coin accumulation, product verification, dispensing, and change return. In[3] its generic FSM design process and HDL modeling techniques are directly applicable. It lays the theoretical and practical groundwork for students to create their own vending machine projects, such as those involving coin handling, product selection, and change dispensing. This work highlights the practical application of FSM concepts in embedded systems, focusing on vending logic that handles coin input, product selection, and change return. The vending machine supports a limited number of products and coin types, using an FSM to track system behaviour through well-defined states such as Idle, Coin Inserted, Product Selected, Dispense Product, and Return Change. The design prioritizes clarity and modularity, which makes it ideal for implementation on FPGAs and educational platforms. What distinguishes Holton's project is its emphasis on hardware deployment rather than just simulation. The design was tested on a physical FPGA development board, demonstrating its real-time performance and reliability. The use of test benches for simulation verification also illustrates best practices in digital system validation. This work is particularly useful for students and developers seeking to transition from simulation-only designs to FPGA-based implementations. It effectively bridges theoretical FSM models with practical HDL deployment making it a strong reference for vending machine automation using digital logic in[4].

Fig.1.1. Vending Machine Prototype

The primary objective of this project is to design and implement a vending machine capable of dispensing items based on user input and providing accurate change when necessary. The system should be efficient, reliable, and cost-effective, utilizing VERILOG for the digital logic design.

**1.3 User Interface:** The vending machine will feature a simple interface with buttons or a touchscreen for product selection. Clear labels and intuitive design will enhance user experience.User Interface: The vending machine will have an intuitive interface that will simply consist of buttons or a touch screen for selection of products. The interface will have clear labels, and be designed to be easy to use by the consumer. Payment system: The vending machine will accept coins, and possibly paper currency. The system will have sensors that will detect, validate, and accept the payment. A coin slot and bill acceptor will be incorporated into the vending machine design. Product Dispensing: The machine will have designated compartments that will store each of the products while the user is selecting and paying for the product. the related compartment would open and the product would be dispensed.Change dispenser: A change dispenser will be build into the system to dispense change accurately. It will calculate the difference between the paid amount and the product price and dispense the coins.

### **1.4 Implementation**

Hardware: The Vending Machine will be constructed of durable materials; comprised of storage compartments for product storage, a coin mechanism, a bill reader, and a mechanism to dispense change. Software: The user interface will be programmed using the appropriate software language(s), C++ or Python. We expect to use algorithms to compute payment processing, product selection and change calculation.

Testing: We will extensively test the Vending Machine to verify its functionality and reliability. We will test the user interface, the payment system, product dispensing system and the change system.

### **1.5 Evalution**

Usability: The usability of the vending machine will be evaluated from user feedback and observations. If any issues arise with either the interface or functionality, those will be resolved.

Reliability: The reliability of the vending machine to dispense products correctly and return change will also be examined through extensive testing and monitoring.

**1.6 Scope:** The project will include the design, implementation, and testing of a vending machine with a change system implemented using VERILOG. This project will involve design of the system architecture, coding in VERILOG, simulation, and onto a hardware manifestation in the FPGA (Field-Programmable Gate Array) platform.

**VERILOG in Digital System Design:** VERILOG is a hardware descriptive language often used to model digital systems and simulate their operation. VERILOG is a very efficient way to describe a digital system design and allows the designer to create functionality in their design fairly easily which makes it very flexible as a design method. VERILOG is frequently used for its flexibility, scalability, and simulation in digital design.

**Development:** Set up the actuators, motors, sensors, microcontrollers, and hardware components. Construct software modules for product dispensation, payment methods, user interface and change computation. Integrate hardware and software together to develop a working vending machine prototype. Test and debug each module iteratively to ensure that it functions correctly.

# **Evaluation and Continuous Improvement:**

Suprise vending machine performance through key performance indicators like revenue, availability and usability. Assess feedback from the operators and users to determine what can be improved. Make improvements or updates using an iterative development process. Constantly monitor vending machine performance and modify as needed to meet changing demands and market conditions. A state diagram provides a useful representation of the behaviour of a vending machine with a change system and an understanding of the transitions to other states. Here's a simplified example of a state diagram showing the feedback loops for state transitions for a vending machine.

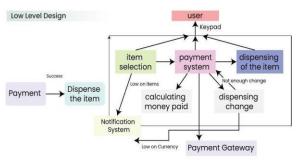

**Overview:** The vending machine with a change system has some main components, including user interface, item dispensing mechanism, a payment system, a change dispenser, and a control unit. These components are all connected to and controlled by the VERILOG based digital logic implemented on an FPGA. The block diagram depicts the functional components of the vending machine system and the relationship among them. It provides a high-level description of the system architecture and the flow of data and control signals.

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

Fig.1.4 FSM (Finite State Machine)

#### Design Methodology

#### Requirements Analysis:

High-level Design: The high-level design activity aims to specify the overall architecture of the system, the functional modules and their connections. It defines the structure and behaviour of the system, which is the basis for a detailed design and implementation.

**VERILOG Implementation:** VERILOG is used to realize the detailed design of the vending machine system. The VERILOG code describes the behavior of each module by defining how each module works and communicates with other modules. Simulation is executed to determine the correctness and functionality of the code produced by VERILOG. Using EDA Playground for the development of a change system for a vending machine consists of using the EDA Playground EDA capabilities for hardware description and simulation.

Fig.2.1. EDA Playground - Simulation Tool

#### **Simulation Setup:**

Start a new project in EDA Playground and choose the right HDL language for your development (Verilog or VERILOG).

Write the hardware description code for each module and save the files in the project folder.

### Simulation and Debugging:

Use EDA Playground's built-in simulation tools to simulate the code Review the simulation results to look for any errors or undesired behaviour in the vending machine's operations Use the same techniques as

prior work to debug the hardware description code and test benches to eliminate errors and ensure the vending machine works as expected

FPGA Selection: Because of its adaptability, reconfigurability, and suitability for digital logic designs, an FPGA platform is selected for hardware implementation.

Fig.2.3 Vending Machine – FSM

# **Design Compilation**

The VERILOG code is synthesized and compiled to the target FPGA platform using vendor-specific design tools. The design constraints are made to maximize power, time, and resource consumption. The design is then mapped to the FPGA for verification and testing after compilation.

### Hardware Testing

Fig.2.4 Arduino-Based Vending Machine Circuit Diagram

Hardware testing is the process of testing for functionality and performance of the vending machine system on the FPGA platform. Functional tests provide testing against operation states of all components in the vending machine system. Functional states include the response of the user processing of payments, and the performance of change dispensing. Performance tests provide testing against throughput, latency and scalability of the vending machine system in different operating conditions.

**Module Descriptions:** Interface Module: Handles user input and system status display. Item Dispenser Module: Dispenses selected items when activated. Payment Module: Manages user payments and calculates users change.Change Module: Dispenses correct change, depending on user payment amount and item cost.Control Unit Module: Controls the operation of the system modules and the state of the system.

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

| EDA                                                                                 | B Ran / Son <sup>®</sup> New separt mails spont/biologrametican. AMD2 Adaptive SoC Network on Obja Register News 27 0 4 Playmonts Log to 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bruget tyre is                                                                      | Balance         Balance <t< th=""></t<>                                                                                  |

| <ul> <li>NOIS &amp; SPRUBERS @</li> <li>Impus Webby 2.9.7</li> </ul>                | Rig chur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Compile Options<br>Hut<br>Run Options<br>Hut Options                                | And safety to be participation of the second se |

| Coper EPKNee after tan Shev output file after tan Download files after tan Examples | A distributive with the helpful for you to revealer your plagramit's deally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Conmunity                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P 157<br>Not weather                                                                | 📕 Q. Sant 👥 📕 🗑 🗮 🖗 🖬 🖗 🖬 🚱 🗑 😵 😵 🔗 🖉 📲 💆 🔺 🕳 🖽 🕫 🕫 🕫 🖉 🖬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# **Simulation Outputs**

**1.** Adding 5 Rs three times consecutively

|              | 0 |     | 10, | 20 | on ne | . 30 |    | 40 |

|--------------|---|-----|-----|----|-------|------|----|----|

|              |   |     |     |    |       |      |    |    |

| clk          |   | 100 |     |    |       |      |    |    |

| in[1:0]      | X | )   |     |    |       |      |    |    |

| cstate[1:0]  | X | þ   |     |    | į.    |      | ¢. |    |

| n_state[1:0] | X | þ   | 1   |    | Þ     |      | þ  |    |

| out          |   |     |     |    |       |      |    |    |

| change[1:0]  | x | þ   |     |    |       |      |    |    |

Fig. 4. output adding 5Rs. Three times consecutively

2. Adding 5 Rs and then 10 Rs.

|              | 0 |   | 10 |    | 20 |    |

|--------------|---|---|----|----|----|----|

|              |   |   |    |    |    |    |

|              |   |   | _  |    |    |    |

| in[1:0]      | X | ) |    | \$ |    |    |

| c_state[1:0] | X | þ |    |    |    | ļ. |

| n_state[1:0] | X | þ |    | į. |    | þ  |

| out          |   |   |    |    |    |    |

| change[1:0]  | X | þ |    |    |    |    |

# 3.Adding 10 Rs two times

Fig.4.2 Output - Adding 10 Rs two times

5.Adding 10 Rs and then nothing

Fig.4.4 Output - Adding 10 Rs and then nothing

4.Adding 5 Rs and then nothing

Fig.4.3 Output - Adding 5 Rs and then nothing

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

**Conclusion:** The design and implementation of the vending machine with change functionality using Verilog was successful in that it could efficiently handle item selection, payments, and change calculation. This project exercised many practical aspects of digital design and provided substantial hands-on experience with hardware description languages. With a modular design approach and testing methodology, the demonstrated system was reliably functional. Not only did this project illustrate the advantages of using Verilog for real-time systems, but it opened up opportunities for future improvements, including acceptance multiple currencies, performance optimizations, and economical design. Overall, this is a strong basis for opportunities for improvements in embedded and automated systems.

**Future Scope: The** vending machine system implemented in Verilog offers a strong foundation for future enhancements. Potential feature additions include support for multiple currency types and remote monitoring for real-time management. Performance can be improved through optimized change calculation algorithms and parallel processing techniques to reduce latency. Cost optimization can be achieved by using more affordable components and streamlining the manufacturing process. These advancements would significantly improve the system's usability, efficiency, and market viability, making it suitable for commercial deployment and further academic exploration.

## References

- S. R. Kumar, A. N. Mehta, V. B. Kumar, "Design of Vending Machine Using Verilog HDL," International Journal of Innovative Research in Science, Engineering and Technology, vol. 13, no. 4, 2024.

- H. Shekhar, V. Kumar, J. K. Choudhary, C. Kumari, S. Oza-Rahurkar, "Implementation of Vending Machine through Verilog HDL," International Journal of Scientific Research & Engineering Trends, vol. 10, no. 2, 2024.

- 3. M. K. Patel, J. P. Soni, R. V. Ramesh, "Design and Implementation of Intelligent Vending Machine Using FSM," The International Journal of Engineering Research, vol. 6, no. 5, 2024.

- 4. M. H. Fuad, R. Yeassin, K. M. Mehedi Hassan, M. Mahamudunnobi Sykot, M. Faysal Nayan, "Design of a Vending Machine Using Verilog HDL and Implementation in Genus & Encounter," European Journal of Electrical Engineering and Computer Science, vol. 7, no. 6, 2023.

- 5. P. C. Datta, C. Vinay Kumar, R. Singh, K. Mummaneni, "Design and Implementation of Vending Machine Using Verilog HDL," International Journal of Creative Research Thoughts, vol. 9, no. 3, 2022.

- 6. H. Shekhar, "Implementation of Vending Machine through Verilog HDL," International Journal of Scientific Research & Engineering Trends (IJSRET), vol. 10, no. 2, 2024

- 7. Suthar, "A Novel Implementation of FPGA Based Smart Vending Machine," in Proc. 2021 IEEE Int. Conf. on Technology, Research, and Innovation for Betterment of Society (TRIBES), 2021.

- 8. J. Guo, Y. Liu, "The Design and Implementation of a Vending Machine Based on State Machine, FPGA, and Microcontroller," in Proc. 2021 IEEE Int. Conf. on Electrical Engineering and Mechatronics Technology (ICEEMT), 2021.

- 9. J. P. Jose, A. S. Nair, S. R. Varma, "Design and Implementation of FPGA based Vending Machine for Integrated Circuits (IC's)," International Journal of Research in Engineering, Science and Management (IJRESM), vol. 5, no. 4, 2023.

- P. C. Datta, C. Vinay Kumar, R. Singh, K. Mummaneni, "Optimized RTL Design of a Vending Machine Through FSM Using Verilog HDL," in Micro and Nanoelectronics Devices, Circuits and Systems, Springer, 2022.

- 11. M. H. Fuad, R. Yeassin, K. M. Hassan, M. M. Sykot, M. F. Nayan, "Design of a Vending Machine Using Verilog HDL and Implementation in Genus & Encounter," European Journal of Electrical Engineering and Computer Science (EJECE), vol. 7, no. 6, 2023.

- 12. V.Hristov, M.Zhilevski, "Approach for Implementation of Vending Machine through Verilog HDL," in Proc. 2022 Int. Congress on Human-Computer Interaction, Optimization and Robotic Applications (HORA), 2022.

- M. A. Qureshi, F. A. Khan, S. B. Ansari, "Design and Implementation of Vending Machine using Verilog HDL," in Proc. 2nd Int. Conf. on Networking and Information Technology, Hong Kong, 2011.