E-ISSN: 2229-7677 • Website: <a href="www.ijsat.org">www.ijsat.org</a> • Email: editor@ijsat.org

# Simulation of Self Balanced Switched Capacitor Based Thirteen Level Inverter

## Shaik Gouse Basha<sup>1\*</sup>, Shabbier Ahmed Sydu<sup>2</sup>

<sup>1</sup>Vignan's LARA Institute of Technology & Science, Department of EEE, India <sup>2</sup>University of Technology and Applied Sciences, E&E Section, Department of Engineering, Oman

#### **Abstract**

The designing of the thirteen level inverter based on switched capacitors with the ability of self-balancing is presented in this article. The proposed inverter converts the low DC voltage into high AC voltage by connecting the switched capacitors in series-parallel. The Phase Disposition modulation scheme with Multi-carrier is developed to generate the switching pulses. The capacitor voltages are balanced itself which improves the performance of the system. As opposite to existing switched-capacitor based inverters, the proposed inverters do not have an H-bridge circuit and the voltage stress of the switches is not exceeded to the supply voltage. The voltage ratings of each mode of operation is realized in mathematically and the harmonic distortions are also observed at different modulation indices. The MATLAB/SIMULINK is used to simulate the inverter and observed the advantages of low peak inverse voltage, total standing voltage, high conversion ability, and high boosting capability.

### **Keywords**

Self-balanced, Switched Capacitor, Multi-carrier based Phase Disposition PWM, Thirteen level Boost inverter, Peak Inverse Voltage (PIV), Total Standing Voltage (TSV).

### 1. Introduction

The demand for quality and reliable power is increasing nowadays for domestic and industrial applications. Therefore, it is necessary to provide quality and reliable power for the utility grids. For uninterrupted power supplies, generally, inverters are preffered. The two level Inverters are not able to produce high voltages without disturbances like harmonics, switching losses. So, Multilevel Inverters are preferred to provide continuous and reliable power for industrial and applications. The advantages such as low voltage stress on the switches, low harmonic distortions, the resemblance of the quality sinusoidal waveform and operating with low switching frequency are increasing its popularity [1].

Multilevel Inverters are used almost in every electrical application such as HVDC applications, energy conversions, electrical vehicles, uninterruptible power supplies, etc. [4]. However, these multilevel inverters are also facing issues sch as high harmonic distortions, high switching and conduction losses. The boost converters, transformers and inductors are not required to boost the voltage in Multilevel Inverters. The inverter topology with H-bridge configuration has different blocking voltage of switches which results the high PIV and TSV. The asymmetric inverter topologies are restricted to certain voltage levels and for more levels the circuit will be complexity and expensive. The voltage balancing of capacitors plays an important role in Multilevel Inverter topologies. The Researchers are focussing on

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

novel topologies that lessen the problems associated with traditional MLIs.

The H-bridge configuration of five level inverter is connected to the utility grid with space vector modulation scheme in [11]. The author proposed single phase seven level inverter with three DC sources in [12]. The topology has auxillary circuit to produce seven level, H-Bridge circuit as main circuit which produces phase shift. The asymmetrical nine level inverter topology is presented in [13]. However, the circuit design and voltage balancing of capacitors is very complexity and difficult. The three capacitors are used The generalized structure of topology [14] has three DC sources with level shift modulation scheme produces the eleven level output.

The multilevel inverters along with switched capacitor is implementing from the past few years to overcome the issues of the existing inverters. The boosting capability of seven-level inverter along with switched-capacitor topology is discussed in [18-19]. The quadruple boosting ability nine-level switched-capacitor based inverter is presented in [20]. The 13-level inverter which is very expensive due to utilizing of four DC sources in [21]. The two DC sources, two capacitors, and few power switches to generate the 13 level inverter in [22]. The fifteen level inverter is discussed in [23] with four DC sources that lead to complexity and expense. The multiport switched-capacitor based multilevel inverter [24] with H-bridge connection which results high switching stress and total standing voltage.

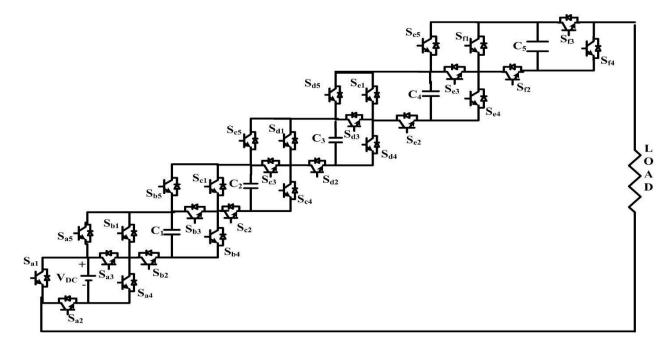

### 2. Thirteen Level Inverter based on Switched Capacitor

The thirteen level inverter based on switched-capacitor consists of a cascaded connection of five modules, single DC source and five capacitors as shown in Figure.1. Each module comprises the five semi-conductor switches  $S_{a1} - S_{a5}$ .

Figure.1: Thirteen level Inverter based on switched capacitor

The switches  $S_{a2}$  and  $S_{a5}$  are conducting to charge the capacitor by the parallel connection to the input DC source. By conducting the switches  $S_{a2}$  and  $S_{a3}$  will positively discharge the charged capacitor for  $+V_{DC}$ , the switches  $S_{a1}$  and  $S_{a4}$  are conducted to discharge negatively  $-V_{DC}$ . In order to match the input DC

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

voltage, the five capacitors are first completely charged and connected in parallel to the input DC source. The required staircase output will be produced by series discharging the charged capacitors at the selected switching frequency.

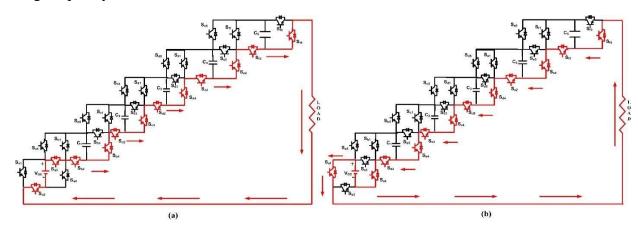

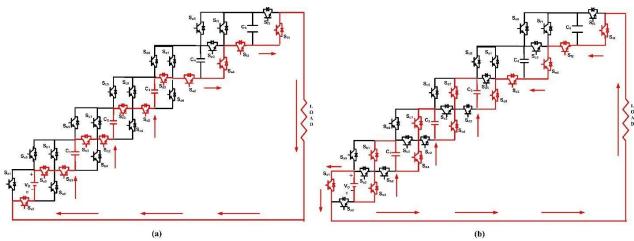

Figure.2: Modes of operation (a) +Vdc, (b) -Vdc

$V_0 = \pm V_{DC}$  state: For  $\pm V_{DC}$  voltage level, the input DC source, seven switches, and five diodes will conduct. The switches  $S_{a3}$ ,  $S_{b2}$ ,  $S_{c2}$ ,  $S_{d2}$ ,  $S_{e2}$ ,  $S_{f2}$ ,  $S_{a2}$  are conducting along with the input DC voltage to obtain  $+V_{DC}$  voltage as shown in Figure 2(a). Similarly, the switches  $S_{a1}$ ,  $S_{f4}$ ,  $S_{e4}$ ,  $S_{d4}$ ,  $S_{c4}$ ,  $S_{b4}$ ,  $S_{a4}$  will conduct to obtain  $-V_{DC}$  voltage as represented in Figure 2(b).

Figure 3: Modes of operation (a) +2Vdc, (b) -2Vdc

$V_0 = \pm 2V_{DC}$  **state:** The remaining capacitors,  $C_2$  through  $C_5$ , are in parallel to the DC source in this state, while the capacitor  $C_1$  is in series with the input DC source. The  $2V_{DC}$  voltage is obtained by adding the capacitor voltage  $V_{C1}$  to the input voltage  $V_{in}$ . Figure 3(a) illustrates how the eight switches  $S_{a3}$ ,  $S_{b2}$ ,  $S_{b3}$ ,  $S_{c2}$ ,  $S_{d2}$ ,  $S_{e2}$ ,  $S_{f2}$ ,  $S_{a2}$ , work in conduction to produce the  $+2V_{DC}$  voltage level. Likewise, as seen in Figure 3(b), the switches  $S_{a1}$ ,  $S_{f4}$ ,  $S_{e4}$ ,  $S_{d4}$ ,  $S_{c4}$ ,  $S_{b4}$ ,  $S_{b1}$ ,  $S_{a4}$  are operated to determine the  $-2V_{DC}$  voltage level.

$$V0 = Vin + VC1 = VDC + VDC = 2VDC$$

(1)

E-ISSN: 2229-7677 • Website: <a href="www.ijsat.org">www.ijsat.org</a> • Email: editor@ijsat.org

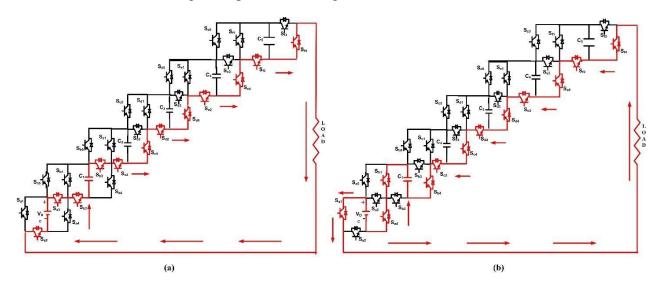

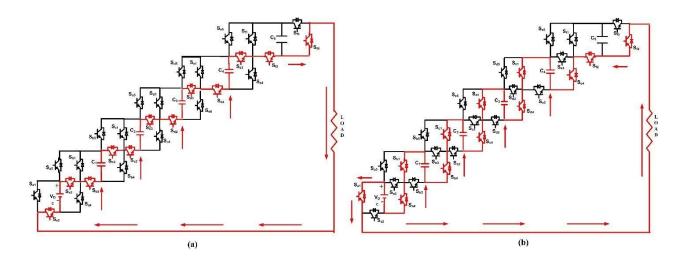

Figure 4: Modes of operation (a) +3Vdc, (b) -3Vdc

$V_0 = \pm 3V_{DC}$ : The input DC source is connected to the capacitors  $C_1 - C_2$  in series and  $C_3 - C_5$  in parallel. In order to get the  $3V_{DC}$  voltage in this state, the input voltage  $V_{in}$  is increased by the capacitor voltages  $V_{C1}$  and  $V_{C2}$ , and current flows through nine switches and three diodes. For  $\pm 3V_{DC}$ , the switches  $S_{a3}$ ,  $S_{b2}$ ,  $S_{b3}$ ,  $S_{c2}$ ,  $S_{c3}$ ,  $S_{d2}$ ,  $S_{e2}$ ,  $S_{f2}$ ,  $S_{a2}$  will conduct as shown in Figure 4(a), and for  $\pm 3V_{DC}$ , the switches  $S_{a1}$ ,  $S_{f4}$ ,  $S_{e4}$ ,  $S_{c4}$ ,  $S_{c4}$ ,  $S_{c4}$ ,  $S_{c1}$ ,  $S_{b4}$ ,  $S_{b1}$ ,  $S_{a4}$  are in ON state as presented in Figure 4(b).

$$V_0 = V_{in} + V_{C1} + V_{C2} = V_{DC} + V_{DC} + V_{DC} = 3V_{DC}$$

(2)

Figure 5: Modes of operation (a) +4Vdc, (b) -4Vdc

$V_0 = \pm 4V_{DC}$ : To generate the  $\pm 4V_{DC}$  level, the three capacitors  $C_1 - C_3$  are connected in series with the input DC source to discharge the capacitor voltages through the ten switches and two diodes. At the same time, the remaining capacitors  $C_4 - C_5$  is connected in parallel with DC source to charge the capacitors. The switches  $S_{a3}$ ,  $S_{b2}$ ,  $S_{b3}$ ,  $S_{c2}$ ,  $S_{c3}$ ,  $S_{d2}$ ,  $S_{d3}$ ,  $S_{c2}$ ,  $S_{f2}$ ,  $S_{a2}$  will conduct for  $\pm 4V_{DC}$  as in Figure 5(a), and the switches  $S_{a1}$ ,  $S_{f4}$ ,  $S_{c4}$ ,  $S_{d4}$ ,  $S_{d1}$ ,  $S_{c4}$ ,  $S_{c1}$ ,  $S_{b4}$ ,  $S_{b1}$ ,  $S_{a4}$  are in ON state to generate  $\pm 4V_{DC}$  as Figure 5(b).

$$V_0 = V_{in} + V_{C1} + V_{C2} + V_{C3} = V_{DC} + V_{DC} + V_{DC} + V_{DC} = 4V_{DC}$$

(3)

E-ISSN: 2229-7677 • Website: <a href="www.ijsat.org">www.ijsat.org</a> • Email: editor@ijsat.org

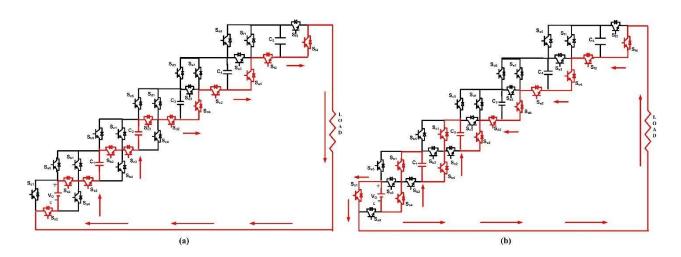

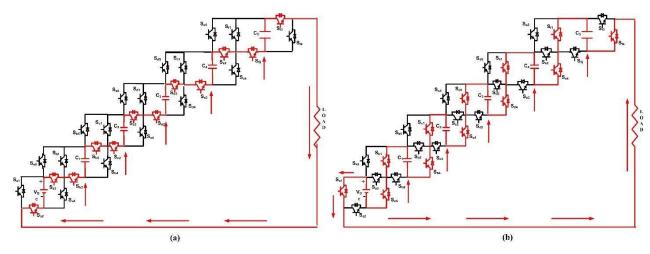

Figure 6: Modes of operation (a) +5Vdc, (b) -5Vdc

$V_0 = \pm 5 V_{DC}$ : The capacitors  $C_1 - C_4$  are connected in series and are discharged through the eleven switches  $S_{a3}$ ,  $S_{b2}$ ,  $S_{b3}$ ,  $S_{c2}$ ,  $S_{c3}$ ,  $S_{d2}$ ,  $S_{d3}$ ,  $S_{e2}$ ,  $S_{e3}$ ,  $S_{f2}$ ,  $S_{a2}$ , and a diode to produce  $+5 V_{DC}$  level as displayed in Figure 6(a). Similarly, the switches  $S_{a1}$ ,  $S_{f4}$ ,  $S_{e4}$ ,  $S_{e1}$ ,  $S_{d4}$ ,  $S_{d1}$ ,  $S_{c4}$ ,  $S_{c1}$ ,  $S_{b4}$ ,  $S_{b1}$ ,  $S_{a4}$  will conduct for  $-5 V_{DC}$  level as displayed in Figure 6(b).

$$V_0 = V_{in} + V_{C1} + V_{C2} + V_{C3} + V_{C4} = V_{DC} + V_{DC} + V_{DC} + V_{DC} + V_{DC} = 5V_{DC}$$

(4)

$V_0 = \pm 6 V_{DC}$ : The five capacitors  $C_1 - C_5$  completely discharges and combined with the input voltage to produce  $6 V_{DC}$  level. For  $+6 V_{DC}$ , the switches  $S_{a3}$ ,  $S_{b2}$ ,  $S_{b3}$ ,  $S_{c2}$ ,  $S_{c3}$ ,  $S_{d2}$ ,  $S_{d3}$ ,  $S_{e2}$ ,  $S_{e3}$ ,  $S_{f2}$ ,  $S_{f3}$ ,  $S_{a2}$  will conduct as shown in Figure 7(a). Similarly, for  $-6 V_{DC}$ , the switches  $S_{a1}$ ,  $S_{f4}$ ,  $S_{f1}$ ,  $S_{e4}$ ,  $S_{e1}$ ,  $S_{d4}$ ,  $S_{d1}$ ,  $S_{c4}$ ,  $S_{c1}$ ,  $S_{b4}$ ,  $S_{b1}$ ,  $S_{a4}$  will conducts as shown in Figure 7(b).

$$V_0 = V_{in} + V_{C1} + V_{C2} + V_{C3} + V_{C4} + V_{C5} = V_{DC} + V_{DC} + V_{DC} + V_{DC} + V_{DC} + V_{DC} = 6V_{DC}$$

Figure 7: Modes of operation (a) +6Vdc,b) -6Vdc

E-ISSN: 2229-7677 • Website: <a href="www.ijsat.org">www.ijsat.org</a> • Email: editor@ijsat.org

Table 1. Positions of switches, diodes, and capacitors for each level.

| Desired<br>Level  | Operating Switches                 | Operating Diodes                  | Capacitors State |                |                |                |                |

|-------------------|------------------------------------|-----------------------------------|------------------|----------------|----------------|----------------|----------------|

|                   |                                    |                                   | C <sub>1</sub>   | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> |

| +V <sub>dc</sub>  | Sa3, Sb2, Sc2, Sd2, Se2,           | Sb4, Sc4, Sd4, Se4,               | 1                | 1              | 1              | 1              | 1              |

|                   | $S_{f2}, S_{a2}$                   | Sf4                               |                  |                |                |                |                |

| +2V <sub>dc</sub> | Sa3, Sb2, Sb3, Sc2, Sd2,           | Sc4, Sd4, Se4, Sf4                | $\downarrow$     | 1              | <b>↑</b>       | 1              | 1              |

|                   | Se2, Sf2,                          |                                   |                  |                |                |                |                |

|                   | $S_{a2}$                           |                                   |                  |                |                |                |                |

| +3V <sub>dc</sub> | Sa3, Sb2, Sb3, Sc2, Sc3,           | Sd4, Se4, Sf4                     | $\downarrow$     | $\downarrow$   | <b>↑</b>       | 1              | 1              |

|                   | $S_{d2}, S_{e2}, S_{f2}, S_{a2}$   |                                   |                  |                |                |                |                |

| +4V <sub>dc</sub> | Sa3, Sb2, Sb3, Sc2, Sc3,           | Se4, Sf4                          | $\downarrow$     | $\downarrow$   | $\downarrow$   | 1              | 1              |

|                   | Sd2, Sd3, Se2, Sf2, Sa2            |                                   |                  |                |                |                |                |

| +5V <sub>dc</sub> | Sa3, Sb2, Sb3, Sc2, Sc3,           | Sf4                               | $\downarrow$     | $\downarrow$   | $\downarrow$   | $\downarrow$   | 1              |

|                   | Sd2, Sd3, Se2, Se3, Sf2,           |                                   |                  |                |                |                |                |

|                   | $S_{a2}$                           |                                   |                  |                |                |                |                |

| +6V <sub>dc</sub> | Sa3, Sb2, Sb3, Sc2, Sc3,           |                                   | $\downarrow$     | $\downarrow$   | $\downarrow$   | $\downarrow$   | $\downarrow$   |

|                   | Sd2, Sd3, Se2, Se3, Sf2,           |                                   |                  |                |                |                |                |

|                   | Sf3, Sa2                           |                                   |                  |                |                |                |                |

| -6V <sub>dc</sub> | Sa1, Sf4, Sf1, Se4, Se1,           |                                   | $\downarrow$     | $\downarrow$   | $\downarrow$   | $\downarrow$   | $\downarrow$   |

|                   | Sd4, Sd1, Sc4, Sc1, Sb4,           |                                   |                  |                |                |                |                |

|                   | $S_{b1}, S_{a4}$                   |                                   |                  |                |                |                |                |

| -5V <sub>dc</sub> | Sa1, Sf4, Se4, Se1, Sd4,           | Sf2                               | $\downarrow$     | $\downarrow$   | $\downarrow$   | $\downarrow$   | 1              |

|                   | Sd1, Sc4, Sc1, Sb4, Sb1,           |                                   |                  |                |                |                |                |

|                   | Sa4                                |                                   |                  |                |                |                |                |

| -4V <sub>dc</sub> | Sa1, Sf4, Se4, Sd4, Sd1,           | $S_{f2}$ , $S_{e2}$ ,             | $\downarrow$     | $\downarrow$   | $\downarrow$   | 1              | 1              |

|                   | Sc4, Sc1, Sb4, Sb1, Sa4            |                                   |                  |                |                |                |                |

| -3V <sub>dc</sub> | Sa1, Sf4, Se4, Sd4, Sc4,           | Sf2, Se2, Sd2                     | $\downarrow$     | $\downarrow$   | 1              | 1              | 1              |

|                   | Sc1, Sb4, Sb1, Sa4                 |                                   |                  |                |                |                |                |

| -2V <sub>dc</sub> | Sa1, Sf4, Se4, Sd4, Sc4,           | Sf2, Se2, Sd2, Sc2                | $\downarrow$     | 1              | <b>↑</b>       | <b>↑</b>       | 1              |

|                   | Sb4, Sb1,                          |                                   |                  |                |                |                |                |

|                   | Sa4                                |                                   |                  |                |                |                |                |

| -V <sub>dc</sub>  | Sa1, Sf4, Se4, Sd4, Sc4,           | $S_{f2}, S_{e2}, S_{d2}, S_{c2},$ | <u> </u>         | <u></u>        | 1              | 1              | 1              |

|                   | S <sub>b</sub> 4, S <sub>a</sub> 4 | Sb2                               | 1                |                |                | 1              | 1              |

### 4. Results and Discussion

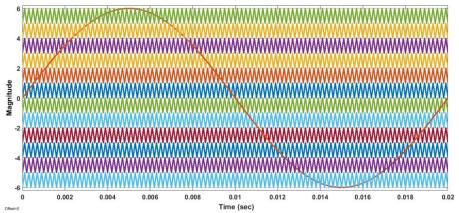

The MATLAB/SIMULINK software is used to implement the thirteen-level inverter based on switched capacitors. The Switched Capacitors have the ability to sustained the voltage  $V_{DC}$ . The multicarrier

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

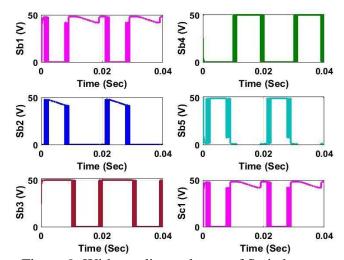

signals have frequency of 20KHZ are matched with the Sinusoidal reference signal of 50Hz to generate the switching pulses of the proposed inverter as shown in Figure 8.

Figure 8: Waveform of Phase Disposition Modulation

Figure 9: Withstanding voltages of Switches

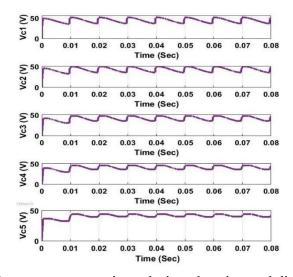

Figure 10: Voltage across capacitors during charging and discharging.

The thirteen-level output is obtained by applying the generated switching pulses to the inverter. The switches have the ability to sustained the voltage throughout the turn-on and off process. Furthermore, the

•

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

sustained voltage of each switch is same as applied voltage of 50V as displayed in Figure 9. The self-balancing technique is used to charge and discharge the switched capacitors. As illustrated in Figure 10, each capacitor discharges a 50V voltage when connected in series with the input DC voltage. Table 2. Specifications.

| Terms                              | Ratings         |  |  |  |

|------------------------------------|-----------------|--|--|--|

| Applied Voltage (V <sub>DC</sub> ) | 50V             |  |  |  |

| Desired voltage                    | 250V            |  |  |  |

| Switched Capacitors                | 5               |  |  |  |

| Boosting Capability                | 5 Times         |  |  |  |

| Peak Inverse Voltage (PIV)         | $1V_{DC}$       |  |  |  |

| Switches used                      | 29              |  |  |  |

| Sustained voltage of each switch   | V <sub>DC</sub> |  |  |  |

| Switching Frequency                | 20 KHz          |  |  |  |

| Obtained output levels             | 13              |  |  |  |

| Output Current                     | 4.8 A           |  |  |  |

| Resistor                           | 50Ω             |  |  |  |

| Inductor                           | 10mH            |  |  |  |

| Total Standing Voltage (TSV)       | $5V_{DC}$       |  |  |  |

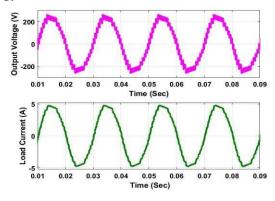

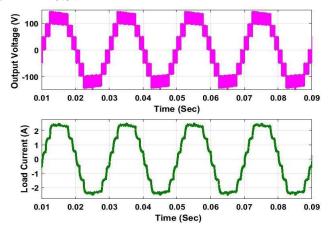

As seen in Figure 11, this suggested inverter generated thirteen levels of output of 250V and 4.8A respectively, with the application of 50V, the frequency and capacitor are being 50Hz and  $1000\mu F$  to the load at modulation index MI = 1.

Figure 11: Performance of inverter at MI = 1.

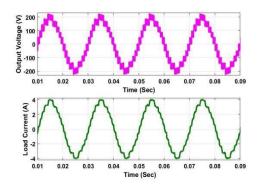

As shown in Figure 12, this suggested inverter generated eleven levels of 210V and 3.9A respectively, with the applied voltage of 50V, the frequency and capacitor are being 50Hz and  $1000\mu\text{F}$  to the load at modulation index MI = 0.7

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

Figure 12 : Performance of inverter at MI = 0.7.

From the Figure 13, this suggested inverter generated seven levels of output of 140V and 2.4A respectively, with the applied voltage of 50V, the frequency and capacitor are being 50Hz and  $1000\mu F$  to the load at modulation index MI = 0.5.

Figure 13: Performance of inverter at MI = 0.5.

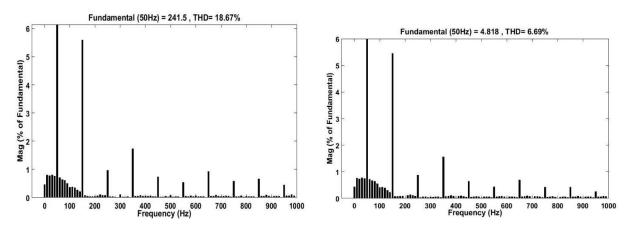

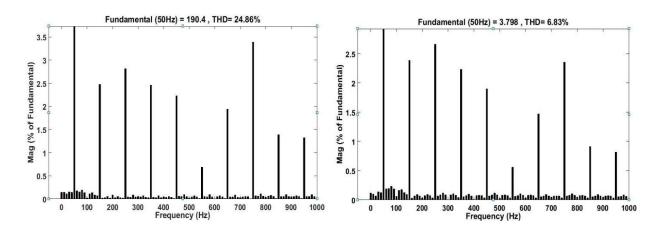

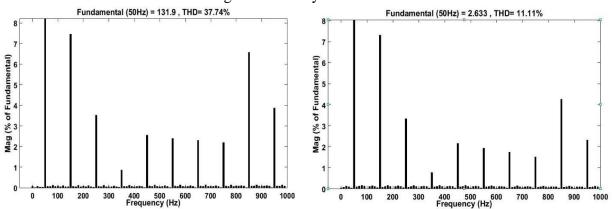

The harmonic distortion analysis of proposed thirteen level inverter at different modulation indices are displayed in Figure 14, 15 and 16.

Figure 14: Analysis of THD at MI = 1.

E-ISSN: 2229-7677 • Website: <a href="www.ijsat.org">www.ijsat.org</a> • Email: editor@ijsat.org

Figure 15: Analysis of THD at MI = 0.7.

Fig. 16: Analysis of THD at MI = 0.5.

### 5. Conclusion

The new assembly of thirteen level multilevel inverters is presented and simulated in this article. The proposed inverter converts the DC – AC by employing a single DC source and achieves the high boosting capability using switched capacitor technique. The detailed modes of operation is discussed. The capacitor voltages are balanced itself by using multi-carrier based phase disposition PWM control scheme. The switches are operated at the same frequency which results in the low conduction and switching losses. Due to not having an H-bridge circuit in the proposed inverter, the voltage stress of the switches is equal to  $V_{DC}$  which results in the low PIV and TSV. Finally, for various modulation indexes, the simulation results demonstrate the feasibility and competence of the inverter.

#### References

- Siddique, Marif & Mekhilef, Saad & Shah, Noraisyah & Sarwar, Adil & Iqbal, Atif & Memon, Mudasir. (2019). "A New Multilevel Inverter Topology With Reduced Switch Count. IEEE Access. PP. 1-1. 10.1109/ACCESS.2019.2914430.

- 2. Sze Sing Lee, "Single-Stage Switched-Capacitor Module (S3CM)Topology for Cascaded Multilevel Inverter", IEEE Transactions on Power Electronics, 2018.

- 3. Jahan, H. K.; Abapour, M.; Zare, K.; Hosseini, S. H.; Blaabjerg, F.; Yang, Y, "A Multilevel Inverter with Minimized Components Featuring Self-balancing and Boosting Capabilities for PV Applications", IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020.

E-ISSN: 2229-7677 • Website: www.ijsat.org • Email: editor@ijsat.org

- 4. Ahad Rasulkhani, AsgharTaheri, "A New Multilevel Inverter Topology with Component Count Reduction", International Journal of Industrial Electronics, Control and Optimization, Vol. 2, No. 4, pp. 355-364, Oct 2019.

- 5. Ronak A. Rana, Sujal A. Patel, Anand Muthusamy, Chee woo Lee, and Hee-Je Kim, "Review of Multilevel Voltage Source Inverter Topologies and Analysis of Harmonics Distortions in FC-MLI", Electronics 2019, 8, 1329; doi:10.3390/electronics8111329.

- Ahmad Behzadi Nezhad, Alireza Namadmalan & Ali Rahdarian (2019): Cascaded H-Bridge Multilevel Inverters with Discrete Variation of DC Sources, International Journal of Electronics, DOI: 10.1080/00207217.2019.1600736.

- 7. Ranjith Kumar Kalilasam, Venkatesan Mani, "FPGA based quasi z-source cascaded multilevel inverter using multicarrier PWM techniques", JOURNAL OF VIBROENGINEERING, VOLUME 20, ISSUE 3, MAY 2018.

- 8. Jeby Thomas Jacob, D. Kirubakaran, "A Hybrid T-Type Multilevel Inverter With A Novel Modulation Strategy For Isolated Supply Electric Systems", Journal of Engineering Science and Technology Vol. 14, No. 3 (2019) 1614 1638.

- 9. Tarmizi Tarmizi, Soib Taib, and M. K. Mat Desa, "Design and Verification of Improved Cascaded Multilevel Inverter Topology with Asymmetric DC Sources", Journal of Power Electronics, Vol. 19, No. 5, pp. 1074-1086, September 2019.

- 10. Seyed Hadi Latifi Majareh, Farzad Sedaghati, Majid Hosseinpour, Seyed Reza Mousavi-Aghdam, "Design, analysis and implementation of a generalised topology for multilevel inverters with reduced circuit devices", IET Power Electronics 2019.

- 11. M. Venkatesan, R. Rajeswari, N. Deverajan, "A Fuzzy Logic Based Three phase Inverter with Single DC Source for Grid Connected PV System Employing Three Phase Transformer", INTERNATIONAL JOURNAL of RENEWABLE ENERGY RESEARCH, Vol.5, No.3, 2015.

- 12. Cathrine E. S.Feloups, Ahmed I. M. Ali, Essam E. M. Mohamed, "Design of Single-Phase Seven-Level Inverter with Reduced Number of Switching Devices for PV Applications", Nineteenth International Middle East Power Systems Conference (MEPCON), Menoufia University, Egypt, 19-21 December 2017.

- 13. N. Sandeep, Udaykumar R. Yaragatti," Operation and Control of a Nine-Level Modified ANPC Inverter Topology With Reduced Part Count for Grid-Connected Applications", IEEE Transactions on Industrial Electronics, Vol. 65, No. 6, June 2018.

- 14. S. G. Basha, V. Mani and S. Mopidevi, "Single-phase Thirteen-level Dual-boost Inverter Based Shunt Active Power Filter Control Using Resonant and Fuzzy Logic Controllers," in CSEE Journal of Power and Energy Systems, vol. 8, no. 3, pp. 849-863, May 2022, doi: 10.17775/CSEEJPES.2020.02640...

- 15. E. Babaei and S. S. Gowgani, "Hybrid Multilevel Inverter Using Switched Capacitor Units," IEEE Trans. Ind. Electron., vol. 61, no. 9, pp. 4614-4621, Sept. 2014.

- 16. J. Liu, K. W. E. Cheng and Y. Ye, "A Cascaded Multilevel Inverter Based on Switched- Capacitor for HighFrequency AC Power Distribution System," IEEE Trans. Power Electron., vol. 29, no. 8, pp. 4219-4230, Aug. 2014.

- 17. Liangzong He, Chen Cheng, "A Flying-Capacitor- Clamped Five-Level Inverter Based on Bridge Modular Switched-Capacitor Topology", IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 63, NO. 12, DECEMBER 2016.

- 18. W. Peng, Q. Ni, X. Qiu and Y. Ye, "Seven-Level Inverter with Self- Balanced Switched-Capacitor

E-ISSN: 2229-7677 • Website: <a href="www.ijsat.org">www.ijsat.org</a> • Email: editor@ijsat.org

and Its Cascaded Extension," IEEE Trans. Power Electron., vol. 34, no. 12, pp. 11889-11896, Dec. 2019.

- 19. J. Liu, X. Zhu and J. Zeng, "A Seven-level Inverter with Self-balancing and Low Voltage Stress," IEEE J. Emerg. Sel. Topics Power Electron. vol. 8, no. 1, pp. 685-696, March 2020.

- 20. N. Sandeep, Jagabar Sathik Mohammed Ali, Udaykumar R. Yaragatti, and Krishnasamy Vijayakumar, "Switched-Capacitor-Based Quadruple-Boost Nine-Level Inverter", IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 34, NO. 8, AUGUST 2019.

- 21. E. Samadaei, S. A. Gholamian, A. Sheikholeslami and J. Adabi, "An Envelope Type (E-Type) Module: Asymmetric Multilevel Inverters With Reduced Components," IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7148-7156, Nov. 2016.

- 22. E. Samadaei, M. Kaviani and K. Bertilsson, "A 13-Levels Module (K-Type) With Two DC Sources for Multilevel Inverters," IEEE Trans. Ind. Electron., vol. 66, no. 7, pp. 5186-5196, July 2019.

- 23. Siddique, Marif & Mekhilef, Saad & Shah, Noraisyah & Sarwar, Adil & Iqbal, Atif & Memon, Mudasir. (2019). A New Multilevel Inverter Topology With Reduced Switch Count. IEEE Access. PP. 1-1. 10.1109/ACCESS.2019.2914430.

- 24. S. Raghu Raman, Yat Chi Fong, Yuanmao Ye, and Ka Wai Eric Cheng, "Family of Multiport SwitchedCapacitor Multilevel Inverters for High-Frequency AC Power Distribution", IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 34, NO. 5, MAY 2019.

- 25. Shaik Gouse Basha, Venkatesan M, Mopidevi, S. (2020). An improved single phase self-balancing switched capacitor based step-up nine level inverter. Journal Européen des Systèmes Automatisés, Vol. 53, No. 2, pp. 249- 257. https://doi.org/10.18280/jesa.530212

- 26. Abolfazl Babaie, Bagher Karami, Adib Abrishamifar, "Improved Equations of Switching Loss and Conduction Loss in SPWM Multilevel Inverters", 7th Power Electronics, Drive Systems & Technologies Conference (PEDSTC 2016).